Este é um novo um gerador de funções alimentado e controlado por USB, que segue o mesmo conceito do gerador de funções GF1 apresentado anteriormente (veja os posts de 17 de Agosto do ano passado e 16 de Abril deste ano), embora tenha características muito distintas e uma prestação superior em todos os aspectos. O GF2 é capaz de gerar sinais sinusoidais e triangulares com frequência até 2MHz e amplitude até 8Vpp, sem redução assinalável do desempenho. O ajuste em frequência faz-se em passos de apenas 298mHz, ao passo que a amplitude é ajustável em incrementos de 7,8mV, o que possibilita um controlo paramétrico bastante fino. Para além da frequência e da amplitude, é possível ajustar a fase do sinal gerado. À semelhança do GF1, este gerador de funções pode ser empregue como gerador de relógio, uma vez que possui uma saída digital síncrona.

Parâmetros de funcionamento:

– V d. mín. = 3,66V

– V d. nom. = 5V

– V d. máx. = 5,45V

– Z L mín. = 50Ω

Características eléctricas:

– I d. (Z L = 50Ω@0V) = 132,0mA

– I d. (Z L > 100KΩ) = 82,36mA

– P (Z L = 50Ω@0V) = 660,2mW

– P (Z L > 100KΩ) = 411,8mW

Características da saída analógica:

– Frequência máxima: 2MHz

– Incremento em frequência: 298mHz

– Amplitude máxima (Z L = 50Ω@0V): 4,01Vpp

– Amplitude máxima (Z L > 100KΩ): 8,02Vpp

– Incremento em amplitude (Z L = 50Ω@0V): 3,92mVpp

– Incremento em amplitude (Z L > 100KΩ): 7,83mVpp

– Impedância de saída (Z S): 49,9Ω

Características da saída digital:

– Frequência máxima: 25MHz

– Incremento em frequência: 298mHz

– Razão cíclica: 0,5

– Amplitude (Z L = 50Ω@0V): 2,13Vpp

– Amplitude (Z L = 50Ω@1,65V): 2,32Vpp

– Amplitude (Z L > 100KΩ): 3,30Vpp

– Impedância de saída (Z S): 27,5Ω

Outras características:

– Base de tempo: 80MHz±50ppm

– Taxa de amostragem: 80MSa/s

– Resolução do acumulador de fase: 28bit

– Resolução da compensação de fase: 12bit

– Resolução do conversor D/A: 10bit

– Resolução do controlo de amplitude: 10bit

– Tensão de histerese do comparador: 21,4mV

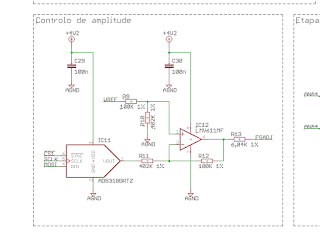

O circuito foi concebido em torno do AD9834 da Analog Devices (IC10). É este o componente responsável pela geração dos sinais, mediante controlo via SPI. Uma das vantagens que o AD9834 oferece relativamente a outros integrados com a mesma função prende-se com o facto de ter saídas complementares, o que permite eliminar o offset com recurso a uma simples subtracção dos respectivos sinais. Outra vantagem deve-se ao facto de o AD9834 ter um pino que possibilita o controlo da amplitude dos sinais gerados, não sendo necessário intervir no caminho dos mesmos. Esse controlo é feito por intermédio do circuito representado na figura seguinte, e cujo funcionamento irei explicar a seguir.

Essencialmente, o que o circuito esquematizado na imagem faz é controlar a corrente debitada através do pino "FS ADJUST" do AD9834 (tensão "FSADJ", no diagrama). Para tal, o AD5310 (IC11), um conversor digital-analógico comandado por SPI, produz uma tensão arbitrária entre 0 e 4,2V. O amplificador operacional LMV611, em IC12, converte o valor da tensão dada pelo AD5310 por forma a que a corrente do pino "FS ADJUST" varie na mesma proporção. Note que a tensão do pino "REFOUT" do AD9834 (tensão "VREF") serve de referência ao circuito, para garantir que a corrente debitada do pino "FS ADJUST" (referenciado internamente pela mesma fonte de tensão) é nula quando a tensão de saída do AD5310 iguala 0V. Quando este último integrado produz a tensão máxima de 4,2V, a corrente debitada do referido pino sobe para aproximadamente 168µA, o que corresponde à amplitude máxima.

Os sinais complementares provenientes do AD9834 passam primeiro por um filtro passa-baixo, ou filtro de reconstrução. Esse filtro, constituído pelos condensadores C31 a C36, pelos indutores L2 a L5, e pelos resistores R14 a R17, elimina os "degraus" resultantes da conversão digital-analógica inerente ao processo de síntese digital directa (ou DDS, sigla de Direct Digital Synthesis), com efeito reconstruindo o sinal. Repare que o filtro é de 5ª ordem com alinhamento próximo a Chebyshev de 0,01dB, visto que não se espera que o gerador de funções produza sinais com mudanças abruptas. Por conseguinte, a fraca resposta em degrau típica deste tipo de filtro não constitui aqui um problema. Os resistores R14, R15, R16 e R17 servem para definir a impedância característica do filtro.

Após a filtragem, os sinais são pré-amplificados por IC13 que, para além de actuar como um amplificador não inversor duplo, também tem o propósito de isolar o filtro da baixa impedância de entrada inerente à etapa posterior. Posteriormente, os sinais são subtraídos um ao outro pelo subtractor que o primeiro amplificador operacional de IC14 integra. Convém sublinhar que os sinais presentes nas entradas do subtractor são complementares e apresentam offset semelhante. Dessa etapa, sai um único sinal, naturalmente amplificado e quase sem offset. Este último sinal é finalmente amplificado pelo segundo amplificador operacional de IC14, e ainda aproveitado para gerar o sinal digital síncrono.

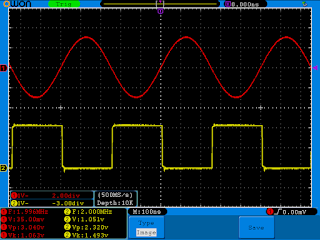

De modo a gerar o referido sinal digital, o sinal analógico que sai do subtractor é processado pelo comparador TLV3501 (IC15), conforme o diagrama da figura abaixo. É importante referir que o comparador mostra uma histerese de cerca de 21mV na sua configuração actual, o que é suficiente para eliminar o ruído e, ao mesmo tempo, gerar um sinal síncrono com pouco jitter. O sinal gerado passa finalmente pelo buffer de relógio em IC16 que, à semelhança do que acontece com o GF1, é o CDCLVC1102 da Texas Instruments.

Os sinais complementares provenientes do AD9834 passam primeiro por um filtro passa-baixo, ou filtro de reconstrução. Esse filtro, constituído pelos condensadores C31 a C36, pelos indutores L2 a L5, e pelos resistores R14 a R17, elimina os "degraus" resultantes da conversão digital-analógica inerente ao processo de síntese digital directa (ou DDS, sigla de Direct Digital Synthesis), com efeito reconstruindo o sinal. Repare que o filtro é de 5ª ordem com alinhamento próximo a Chebyshev de 0,01dB, visto que não se espera que o gerador de funções produza sinais com mudanças abruptas. Por conseguinte, a fraca resposta em degrau típica deste tipo de filtro não constitui aqui um problema. Os resistores R14, R15, R16 e R17 servem para definir a impedância característica do filtro.

Após a filtragem, os sinais são pré-amplificados por IC13 que, para além de actuar como um amplificador não inversor duplo, também tem o propósito de isolar o filtro da baixa impedância de entrada inerente à etapa posterior. Posteriormente, os sinais são subtraídos um ao outro pelo subtractor que o primeiro amplificador operacional de IC14 integra. Convém sublinhar que os sinais presentes nas entradas do subtractor são complementares e apresentam offset semelhante. Dessa etapa, sai um único sinal, naturalmente amplificado e quase sem offset. Este último sinal é finalmente amplificado pelo segundo amplificador operacional de IC14, e ainda aproveitado para gerar o sinal digital síncrono.

De modo a gerar o referido sinal digital, o sinal analógico que sai do subtractor é processado pelo comparador TLV3501 (IC15), conforme o diagrama da figura abaixo. É importante referir que o comparador mostra uma histerese de cerca de 21mV na sua configuração actual, o que é suficiente para eliminar o ruído e, ao mesmo tempo, gerar um sinal síncrono com pouco jitter. O sinal gerado passa finalmente pelo buffer de relógio em IC16 que, à semelhança do que acontece com o GF1, é o CDCLVC1102 da Texas Instruments.

O funcionamento do gerador de funções é controlado na sua totalidade pelo CP2130 da Silicon Labs (IC4). Tal abordagem não é nova, dado que este mesmo interface USB-SPI já foi empregue no gerador de funções GF1. Aspectos como a frequência, a fase e a amplitude são controlados por SPI, operando o CP2130 em modo "mestre". As restantes funcionalidades são controladas por pinos individuais do mesmo interface. A esse respeito, não só é possível ligar e desligar partes do circuito, como também é exequível implementar funções como modulação binária em frequência (BFSK) e fase (BPSK).

O circuito inclui as medidas de protecção habituais contra descargas electrostáticas na alimentação e nas saídas. O dispositivo PolyZen em IC1 oferece protecção contra sobre-tensões, corrente excessiva e surtos na alimentação. Adicionalmente, IC2 e IC3 protegem as linhas do barramento USB contra descargas electrostáticas. Por seu turno, os circuitos de protecção TVS em IC17 e IC18 abrangem as saídas.

O circuito inclui as medidas de protecção habituais contra descargas electrostáticas na alimentação e nas saídas. O dispositivo PolyZen em IC1 oferece protecção contra sobre-tensões, corrente excessiva e surtos na alimentação. Adicionalmente, IC2 e IC3 protegem as linhas do barramento USB contra descargas electrostáticas. Por seu turno, os circuitos de protecção TVS em IC17 e IC18 abrangem as saídas.

Lista de componentes:

C1/2/4-6/21/23/25/27/29/30/37/38/40/42/43/49 – Condensador cerâmico multi-camada 100nF 10V (0805);

C3/9/12/16/18/19/48 – Condensador cerâmico multi-camada 1µF 10V (0805);

C7 – Condensador electrolítico de nióbio NOJA475M006 (NOJA475M006RWJ ou equiv.);

C8 – Condensador electrolítico de nióbio NOJA475M010 (NOJA475M010RWJ ou equiv.);

C10/13/26/28/44/45 – Condensador cerâmico multi-camada 10nF 10V (0805);

C11/14/15/20/46/47 – Condensador cerâmico multi-camada 2,2µF 10V (0805);

C17 – Condensador cerâmico multi-camada 470nF 10V (0805);

C22/24/39/41 – Condensador electrolítico de nióbio NOJA106M006 (NOJA106M006RWJ ou equiv.);

C31/32/35/36 – Condensador cerâmico multi-camada 22pF±5% C0G 10V (0805);

C33/34 – Condensador cerâmico multi-camada 47pF±5% C0G 10V (0805);

D1 – LED WP1503CB/YD;

D2 – LED WP1503CB/ID;

IC1 – Circuito de protecção PolyZen ZEN056V075A48LS;

IC2/3 – Circuito de protecção TVS SP4021-01FTG;

IC4 – Conversor USB-SPI CP2130 (CP2130-F01-GM);

IC5 – Regulador de tensão TPS79933 (TPS79933DDC);

IC6 – Regulador de tensão TPS79942 (TPS79942DDC);

IC7 – Conversor charge-pump LM2776 (LM2776DBV);

IC8 – Regulador de tensão TPS72301 (TPS72301DBV);

IC9 – Oscilador de cristal CTS 636L3C080M00000;

IC10 – Gerador de funções AD9834 (AD9834CRUZ);

IC11 – Conversor digital-analógico AD5310 (AD5310BRTZ);

IC12 – Amplificador operacional LMV611 (LMV611MF);

IC13 – Amplificador operacional OPA2832 (OPA2832ID);

IC14 – Amplificador operacional OPA2830 (OPA2830ID);

IC15 – Comparador TLV3501 (TLV3501AIDBV);

IC16 – Buffer de relógio CDCLVC1102 (CDCLVC1102PW);

IC17 – Circuito de protecção TVS SP4021-01FTG-C;

IC18 – Circuito de protecção TVS SP4020-01FTG;

J1 – Conector USB Molex 67068-9001;

J2/3 – Conector BNC Amphenol RF 112659;

L1/6 – Conta de ferrite MPZ2012S331A (MPZ2012S331AT000);

L2-5 – Indutor MLF2012A1R8J (MLF2012A1R8JT000);

R1/28/30 – Resistor de filme espesso 1MΩ±5% 1/8W (0805);

R2/3/29/31 – Resistor de filme espesso 4,7KΩ±5% 1/8W (0805);

R4/5 – Resistor de filme espesso 82Ω±5% 1/8W (0805);

R6 – Resistor de filme espesso 25,5KΩ±1% 1/8W (0805);

R7 – Resistor de filme espesso 10KΩ±1% 1/8W (0805);

R8 – Resistor de filme espesso 0Ω 1/8W (0805);

R9/12 – Resistor de filme espesso 100KΩ±1% 1/8W (0805);

R10/11 – Resistor de filme espesso 402KΩ±1% 1/8W (0805);

R13 – Resistor de filme espesso 6,04KΩ±1% 1/8W (0805);

R14-17 – Resistor de filme espesso 200Ω±1% 1/8W (0805);

R18/20/23 – Resistor de filme espesso 499Ω±1% 1/8W (0805);

R19/21 – Resistor de filme espesso 1,43KΩ±1% 1/8W (0805);

R22 – Resistor de filme espesso 715Ω±1% 1/8W (0805);

R24 – Resistor de filme espesso 49,9Ω±1% 3/4W (2010);

R25/26 – Resistor de filme espesso 10KΩ±5% 1/8W (0805);

R27 – Resistor de filme espesso 1KΩ±5% 1/8W (0805);

R32/33 – Resistor de filme espesso 10Ω±5% 1/8W (0805).

O layout da placa está disponível nos formatos brd (Eagle 7.7.0) e Gerber. Tratando-se de um layout de quatro camadas, sugiro que a encomenda da placa seja feita através do OSH Park, pois o respectivo desenho foi feito tomando em consideração os requisitos deste serviço. Caso deseje utilizar outro serviço de fabrico, confirme se o mesmo suporta layouts de quatro camadas com furação a partir de 0,5mm. Neste caso em particular, o stackup e os materiais não têm de corresponder aos especificados pelo OSH Park.

A montagem da placa requer equipamento especializado. Os componentes SMD devem ser soldados com recurso a pasta de solda, utilizando o processo de refusão com ar quente. Em primeiro lugar soldam-se os componentes da face superior, e só depois os da face inferior, tendo sempre o cuidado de aplicar o calor estritamente necessário e durante o intervalo de tempo mais curto possível. Os componentes through-hole soldam-se em último lugar, bastando para tal um ferro de soldar comum.

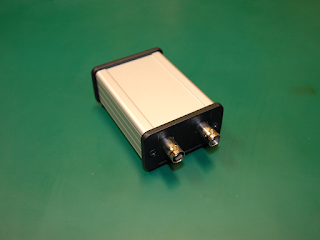

A caixa recomendada para este projecto é a Hammond 1457C801. Trata-se de uma caixa em alumínio anodizado com tampas lacadas a pó preto. Se preferir, pode optar pela caixa 1457C801BK do mesmo fabricante, a qual tem o corpo igualmente lacado a pó preto. A furação das tampas deve ser feita seguindo o guia de furação.

Montado o gerador de funções, é necessário configurar o interface CP2130 do mesmo. Em Windows, isso pode ser feito através da aplicação "CP21xx Customization Utility" da Silicon Labs (a aplicação vem incluída no pacote CP2130_SDK para Windows XP e Vista), utilizando o ficheiro de configuração presente na pasta "Firmware". Se preferir utilizar Linux, deverá utilizar o programa de configuração fornecido no pacote "gf2-r0-conf-1.0.tar.gz", o qual está disponível na pasta "Software". Ambas as pastas, bem como outras pastas e ficheiros relevantes, estão disponíveis na pasta do projecto. Para mais detalhes, veja as notas do projecto.

A montagem da placa requer equipamento especializado. Os componentes SMD devem ser soldados com recurso a pasta de solda, utilizando o processo de refusão com ar quente. Em primeiro lugar soldam-se os componentes da face superior, e só depois os da face inferior, tendo sempre o cuidado de aplicar o calor estritamente necessário e durante o intervalo de tempo mais curto possível. Os componentes through-hole soldam-se em último lugar, bastando para tal um ferro de soldar comum.

A caixa recomendada para este projecto é a Hammond 1457C801. Trata-se de uma caixa em alumínio anodizado com tampas lacadas a pó preto. Se preferir, pode optar pela caixa 1457C801BK do mesmo fabricante, a qual tem o corpo igualmente lacado a pó preto. A furação das tampas deve ser feita seguindo o guia de furação.

Montado o gerador de funções, é necessário configurar o interface CP2130 do mesmo. Em Windows, isso pode ser feito através da aplicação "CP21xx Customization Utility" da Silicon Labs (a aplicação vem incluída no pacote CP2130_SDK para Windows XP e Vista), utilizando o ficheiro de configuração presente na pasta "Firmware". Se preferir utilizar Linux, deverá utilizar o programa de configuração fornecido no pacote "gf2-r0-conf-1.0.tar.gz", o qual está disponível na pasta "Software". Ambas as pastas, bem como outras pastas e ficheiros relevantes, estão disponíveis na pasta do projecto. Para mais detalhes, veja as notas do projecto.

Links importantes:

Diagrama do circuito (pdf): http://app.box.com/s/5l40...wc49

Diagrama do circuito (Eagle 7.7.0 sch): http://app.box.com/s/t7iv...05sp

Layout da placa (pdf): http://app.box.com/s/lk26...ghyn

Layout da placa (Eagle 7.7.0 brd): http://app.box.com/s/809v...kckl

Ficheiros Gerber: http://app.box.com/s/3jh8...92hb

Guia de furação: http://app.box.com/s/etl8...06o2

Firmware (com instruções): http://app.box.com/s/o5tc...2jp2j

Drivers (Windows): http://app.box.com/s/jdkk...g0x4

Software (Linux): http://app.box.com/s/or9s...coor

Notas do projecto: http://app.box.com/s/sccv...cstx

Pasta contendo todos os ficheiros: http://app.box.com/s/w7jt...5kdm

Projecto no OSH Park: http://www.oshpark.com/shared_projects/AIG0zXWz

CP2130_SDK: http://www.silabs.com/.../CP2130_SDK_Windows_XP_Vista.exe

Sem comentários:

Enviar um comentário